Creating an Interrupt Object

A Windows Driver Frameworks (WDF) driver that handles a device’s hardware interrupts must create a framework interrupt object for each interrupt that each device can support. In framework versions 1.11 and later running on WindowsВ 8 or later versions of the operating system, Kernel-Mode Driver Framework (KMDF) and User-Mode Driver Framework (UMDF) drivers can create interrupt objects requiring passive-level handling. Unless you are writing a driver for a System on a Chip (SoC) platform, however, your driver should use DIRQL interrupt objects.

A driver typically creates framework interrupt objects in its EvtDriverDeviceAdd callback function. A driver can also create interrupt objects from its EvtDevicePrepareHardware callback function.

The framework calls the driver’s EvtDriverDeviceAdd callback function before the Plug and Play (PnP) manager has assigned system resources, such as interrupt vectors, to the device. After the PnP manager assigns resources, the framework stores interrupt resources in the device’s interrupt object. (Drivers that do not support Plug and Play cannot use interrupt objects.)

To create a framework interrupt object, your driver must initialize a WDF_INTERRUPT_CONFIG structure and pass it to the WdfInterruptCreate method.

UMDF supports the following types of interrupts:

- Level-triggered (shared or exclusive)

- Edge-triggered (exclusive only)

- MSI (exclusive by definition)

NoteВ В UMDF does not support shared edge-triggered interrupts.

Starting in UMDF version 2.15, UMDF supports interrupts for simple devices like hardware push-buttons, usually backed by GPIO pins, that you cannot enable or disable explicitly using hardware registers. To support such devices, a UMDF driver must use exclusive edge-triggered interrupts.

Starting in KMDF version 1.15, KMDF also supports interrupts for such devices, without the workaround described in Handling Active-Both Interrupts.

Also in WDF_INTERRUPT_CONFIG, your driver supplies pointers to the following driver-supplied event callback functions:

EvtInterruptIsr

Interrupt service routine (ISR) for the interrupt.

EvtInterruptDpc

Deferred procedure call (DPC) for the interrupt.

For drivers using framework version 1.11 or later on WindowsВ 8 or later versions of the operating system, the driver can explicitly set the parent of a framework interrupt object (DIRQL or passive) to either a framework device object or a framework queue object. If the driver specifies a parent, the driver must set the AutomaticSerialization member of the interrupt object’s WDF_INTERRUPT_CONFIG structure to TRUE. (Recall that if AutomaticSerialization is TRUE, the framework synchronizes execution of the interrupt object’s EvtInterruptDpc or EvtInterruptWorkItem callback function with callback functions from other objects that are underneath the interrupt’s parent object.)

As an example, a driver might specify a queue as parent of an interrupt to synchronize the queue’s callbacks with either the interrupt’s EvtInterruptDpc or EvtInterruptWorkItem callback. In this configuration, the framework deletes the queue object when it deletes the device object.

After calling WdfInterruptCreate, the driver can optionally call WdfInterruptSetPolicy or WdfInterruptSetExtendedPolicy to specify additional interrupt parameters. Typically the driver calls these methods from its EvtDriverDeviceAdd callback function.

The framework automatically deletes the interrupt before deleting the interrupt’s parent. Optionally, a driver can call WdfObjectDelete to delete the interrupt at an earlier time.

Supporting Message-signaled Interrupts

Message-signaled interrupts (MSIs) are supported starting with Windows Vista. To enable the operating system to support MSIs for your device, your driver’s INF file must set some values in the registry. For information about how to set these values, see Enabling Message-Signaled Interrupts in the Registry.

Your driver should create a framework interrupt object for each interrupt vector or MSI message that the device can support. If the PnP manager does not grant the device all of the interrupt resources that the device can support, the extra interrupt objects will not be used and their callback functions will not be called.

In WindowsВ 7, the operating system does not support resource requests for more than 910 interrupt messages per device function. In WindowsВ 8, the operating system does not support resource requests for more than 2048 interrupts per device function.

If the device driver exceeds this limit, the device might fail to start. To operate in a computer that contains many logical processors, the driver should not request more than one interrupt per processor.

A driver must tolerate, without failures, system rebalancing of interrupt resources in which the PnP manager assigns to the device any set of alternative interrupt resources from the resource requirements list. For example, the device might be assigned a smaller number of message interrupts than the driver requested. In the worst case, the driver must be prepared to operate the device with just one line-based interrupt.

Message Signaled Interrupts

Message Signaled Interrupts (MSI, Прерывания, инициируемые сообщениями) в PCI версии 2.2 и более поздних, PCI-X, а также в PCI Express — альтернативная форма прерываний: вместо присваивания номера запроса на прерывание, устройству разрешается записывать сообщение по определённому адресу системной памяти, на деле отображенному на аппаратуру локального контроллера прерываний (local APIC) процессора. Для записи сообщения используется тот же механизм захвата шины (bus mastering), что и для DMA.

Для записи сообщений каждое устройство может иметь от одной до тридцати двух уникальных областей памяти.

Все прерывания шины PCI Express всегда доставляются как MSI, даже при использовании эмуляции традиционных номеров проводников прерываний.

- возможность передачи некоторых данных вместе с информацией о наступлении события. Это зачастую избавляет обработчик прерывания от необходимости читать данную информацию из регистров состояния устройства, что уменьшает загрузку шины.

- возможность полного отказа от проводников INT# от устройств и разъемов PCI до главного контроллера прерываний (IO APIC), а также от самого главного контроллера прерываний, упрощает материнскую плату.

- в многопроцессорных и многоядерных системах устройства получают возможность самостоятельно выбирать процессор/ядро для обработки конкретного прерывания, причем делать это полностью на уровне аппаратуры без исполнения программного кода. Это позволяет оптимизировать работу путем размещения большей части структур драйвера устройства и связанного с ним программного обеспечения (сетевых протоколов и т.д.) в кэше конкретного процессора или же в его «ближней» NUMA-памяти.

Поддерживается в операционной системе Microsoft Windows Vista и более поздних, в ОС FreeBSD с версии 6.3, а также в ядре Linux начиная с версии 2.6.8 [1]

Источники

Ссылки

| Это заготовка статьи о компьютерах. Вы можете помочь проекту, исправив и дополнив её. Это примечание по возможности следует заменить более точным. |

Wikimedia Foundation . 2010 .

Смотреть что такое «Message Signaled Interrupts» в других словарях:

Message Signaled Interrupts — Message Signaled Interrupts, in PCI 2.2 and later in PCI Express, are an alternative way of generating an interrupt. Traditionally, a device has an interrupt pin which it asserts when it wants to interrupt the host CPU. While PCI Express does not … Wikipedia

Message-Signaled Interrupts — (MSI) sind eine Art von Interrupts, verfügbar in Computersystemen mit PCI 2.2 und höher. Dabei fordern die MSI fähigen Geräte eine Behandlung nicht über ein elektronisches Signal an, sondern über Nachrichten, die über den PCI Bus an eine… … Deutsch Wikipedia

Interrupt — This article is about computer interrupts. For the study of the effect of disruptions on job performance, see Interruption science. In computing, an interrupt is an asynchronous signal indicating the need for attention or a synchronous event in… … Wikipedia

Conventional PCI — PCI Local Bus Three 5 volt 32 bit PCI expansion slots on a motherboard (PC bracket on left side) … Wikipedia

APIC — Der Advanced Programmable Interrupt Controller (APIC, nicht zu verwechseln mit ACPI) sorgt für die Verteilung von Interrupts in x86 und Itanium basierenden Computersystemen. Der APIC besteht im Gegensatz zum PIC aus zwei Komponenten, dem Local… … Deutsch Wikipedia

Apic — Der Advanced Programmable Interrupt Controller (APIC, nicht zu verwechseln mit ACPI) sorgt für die Verteilung von Interrupts in x86 und Itanium basierenden Computersystemen. Der APIC besteht im Gegensatz zum PIC aus zwei Komponenten, dem Local… … Deutsch Wikipedia

LAPIC — Der Advanced Programmable Interrupt Controller (APIC, nicht zu verwechseln mit ACPI) sorgt für die Verteilung von Interrupts in x86 und Itanium basierenden Computersystemen. Der APIC besteht im Gegensatz zum PIC aus zwei Komponenten, dem Local… … Deutsch Wikipedia

Advanced Programmable Interrupt Controller — Der Advanced Programmable Interrupt Controller (APIC, nicht zu verwechseln mit ACPI) sorgt für die Verteilung von Interrupts in x86 und Itanium basierenden Computersystemen. Der APIC besteht im Gegensatz zum PIC aus zwei Komponenten, dem Local… … Deutsch Wikipedia

Intel APIC Architecture — The Intel APIC Architecture is a system of Advanced Programmable Interrupt Controllers (APICs) designed by Intel for use in Symmetric Multi Processor (SMP) computer systems. It was originally implemented by the Intel 82093AA and 82489DX, and is… … Wikipedia

Программируемый контроллер прерываний — Контроллер прерываний микросхема или встроенный блок процессора, отвечающий за возможность последовательной обработки запросов на прерывание от разных устройств. Английское название Programmable Interrupt Controller (PIC). Как правило… … Википедия

Implement Message Signaled Interrupt in DOS mode

I’m bit stuck at programming device MSI(Message Signaled interrupt) and any pointers welcomed. (my environment is Watcom C + DOS/32a — dos extender, in flat mode. )

@ PIC(8259) mode is ok for me.

I list what I have done as below and maybe someone can help to clarify these. Thanks !

(1) Multiple Message Enable = 0( for single MSI set this field = 0; MMC = 100b)

(2) For MSI message address register in the MSI capability

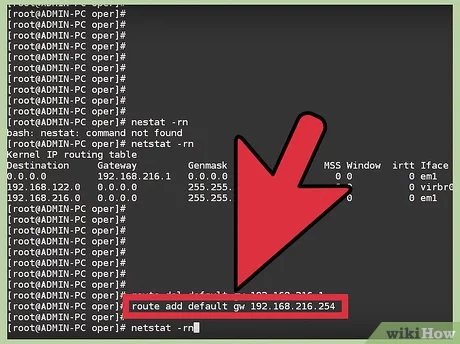

- bit[31:20] = 0xFEE

- bit[19:12] = 0 (Destination ID, and found Local APIC = 0 (Redirection hint = 0)

- bit2 = 0 (Destination Mode, don’t care because of RH = 0)

(3) For MSI message data register in the MSI capability

- bit15 = 0 (trigger mode = edge)

- bit14 = 0 (trigger level, ignored if trigger mode = edge)

- bit[10:8] = 000 (delivery mode = fixed)

- bit[7:0] = 0x20 (vector, and I choose to use 0x20)

(4) Finally enable MSI by setting MSICAP.MC.MSIE = 1

- I have roughly read the doc(chapter 10) http://download.intel.com/products/processor/manual/253668.pdf

- I think there is no need to program IO APIC and Local APIC registers because MSI does not route to APIC system.

Current status: I found system hang after enabling MSIE = 1 and device generates interrupt via MSI !

Note: In above sequence the service routine is NOT installed because I have no idea how to do it. ( is this the reason why my app hang ? )

[20120822 updated] When setting the vector in Message Data field to 0x20, app hang. But if set to 0x76, I found app did not hang and then I can check if device generates interrupt and Local APIC receives this interrupt message as below:

For PCI device(AHCI controller):

- ID(Interrupt Disable) = 0

- IS(Interrupt Status) = 0

- MSI Cap = 09,FEE00000,00000076

For AHCI HBA registers:

- PxIS = 00000023

- PxIE = 7DC0007F

- IS = 00000001

- IE bit1 = 1

By 1 and 2 I think device successfully sends the message to request service because:

- IS bit0 = 1(Port 0 has pending interrupt status)

- IE(Interrupt Enable) = 1

- PCI Command register bit10(ID) = 0

- MSICAP.MC.MSIE = 1(to MSI engine)

Also I found the LAPIC receives this interrupt message because:

- Local APIC IRR(Interrupt Request Register) bit118(=0x76) = 1

- Local APIC ISR(In-Service register) bit118(=0x76) = 1

Thus it seems that device generates the interrupt and Local APIC receives this; even so, my service routine is NOT called !

Message Signaled Interrupts

Message Signaled Interrupts (MSI, Прерывания, инициируемые сообщениями) — альтернативная форма прерываний, доступная в PCI версии 2.2 и более поздних, PCI-X, а также обязательная в PCI Express любых версий. Вместо присваивания фиксированного номера запроса на прерывание, устройству разрешается записывать сообщение по определённому адресу системной памяти, на деле отображенному на аппаратуру локального контроллера прерываний (local APIC) процессора. Для записи сообщения используется тот же механизм захвата шины (bus mastering), что и для DMA.

Содержание

Описание

Для записи сообщений каждое устройство, использующее MSI может иметь от одной до тридцати двух уникальных областей памяти.

Все прерывания шины PCI Express всегда доставляются как MSI, даже при использовании эмуляции традиционных номеров проводников прерываний.

- возможность полного отказа от проводников INT# от устройств и разъемов PCI до главного контроллера прерываний (IO APIC), а также от самого главного контроллера прерываний, что упрощает материнскую плату.

- в многопроцессорных и многоядерных системах устройства, использующие несколько областей MSI, получают возможность самостоятельно выбирать процессор/ядро для обработки конкретного прерывания, причем делать это полностью на уровне аппаратуры без исполнения программного кода. Это позволяет оптимизировать работу путём размещения большей части структур драйвера устройства и связанного с ним программного обеспечения (сетевых протоколов и т.д.) в кэше конкретного процессора или же в его «ближней» NUMA-памяти.

MSI поддерживается в операционных системах Microsoft Windows Vista и более поздних, в ОС FreeBSD с версии 6.3, в ОС OpenBSD с версии 5.0 [1] , а также в ядре Linux начиная с версии 2.6.8 [2]

MSI-X — расширенный вариант MSI, позволяющий определять до нескольких тысяч прерываний.