- Просто о make

- Make- основные сведения

- Простейший Makefile

- Компиляция из множества исходников

- Инкрементная компиляция

- Фиктивные цели

- Переменные

- Автоматические переменные

- How to Write and Run a C Program in Linux

- Step 1: Install the build-essential packages

- Step 2: Write a simple C program

- Step 3: Compile the C program with gcc Compiler

- Step 4: Run the program

- Karim Buzdar

- Linux make command

- Description

- Syntax

- Options

- Typical Use

- Makefiles

- Rules

- Macros

Просто о make

Меня всегда привлекал минимализм. Идея о том, что одна вещь должна выполнять одну функцию, но при этом выполнять ее как можно лучше, вылилась в создание UNIX. И хотя UNIX давно уже нельзя назвать простой системой, да и минимализм в ней узреть не так то просто, ее можно считать наглядным примером количество- качественной трансформации множества простых и понятных вещей в одну весьма непростую и не прозрачную. В своем развитии make прошел примерно такой же путь: простота и ясность, с ростом масштабов, превратилась в жуткого монстра (вспомните свои ощущения, когда впервые открыли мэйкфайл).

Мое упорное игнорирование make в течении долгого времени, было обусловлено удобством используемых IDE, и нежеланием разбираться в этом ‘пережитке прошлого’ (по сути — ленью). Однако, все эти надоедливые кнопочки, менюшки ит.п. атрибуты всевозможных студий, заставили меня искать альтернативу тому методу работы, который я практиковал до сих пор. Нет, я не стал гуру make, но полученных мною знаний вполне достаточно для моих небольших проектов. Данная статья предназначена для тех, кто так же как и я еще совсем недавно, желают вырваться из уютного оконного рабства в аскетичный, но свободный мир шелла.

Make- основные сведения

make — утилита предназначенная для автоматизации преобразования файлов из одной формы в другую. Правила преобразования задаются в скрипте с именем Makefile, который должен находиться в корне рабочей директории проекта. Сам скрипт состоит из набора правил, которые в свою очередь описываются:

1) целями (то, что данное правило делает);

2) реквизитами (то, что необходимо для выполнения правила и получения целей);

3) командами (выполняющими данные преобразования).

В общем виде синтаксис makefile можно представить так:

То есть, правило make это ответы на три вопроса:

Несложно заметить что процессы трансляции и компиляции очень красиво ложатся на эту схему:

Простейший Makefile

Предположим, у нас имеется программа, состоящая всего из одного файла:

Для его компиляции достаточно очень простого мэйкфайла:

Данный Makefile состоит из одного правила, которое в свою очередь состоит из цели — «hello», реквизита — «main.c», и команды — «gcc -o hello main.c». Теперь, для компиляции достаточно дать команду make в рабочем каталоге. По умолчанию make станет выполнять самое первое правило, если цель выполнения не была явно указана при вызове:

Компиляция из множества исходников

Предположим, что у нас имеется программа, состоящая из 2 файлов:

main.c

Makefile, выполняющий компиляцию этой программы может выглядеть так:

Он вполне работоспособен, однако имеет один значительный недостаток: какой — раскроем далее.

Инкрементная компиляция

Представим, что наша программа состоит из десятка- другого исходных файлов. Мы вносим изменения в один из них, и хотим ее пересобрать. Использование подхода описанного в предыдущем примере приведет к тому, что все без исключения исходные файлы будут снова скомпилированы, что негативно скажется на времени перекомпиляции. Решение — разделить компиляцию на два этапа: этап трансляции и этап линковки.

Теперь, после изменения одного из исходных файлов, достаточно произвести его трансляцию и линковку всех объектных файлов. При этом мы пропускаем этап трансляции не затронутых изменениями реквизитов, что сокращает время компиляции в целом. Такой подход называется инкрементной компиляцией. Для ее поддержки make сопоставляет время изменения целей и их реквизитов (используя данные файловой системы), благодаря чему самостоятельно решает какие правила следует выполнить, а какие можно просто проигнорировать:

Попробуйте собрать этот проект. Для его сборки необходимо явно указать цель, т.е. дать команду make hello.

После- измените любой из исходных файлов и соберите его снова. Обратите внимание на то, что во время второй компиляции, транслироваться будет только измененный файл.

После запуска make попытается сразу получить цель hello, но для ее создания необходимы файлы main.o и hello.o, которых пока еще нет. Поэтому выполнение правила будет отложено и make станет искать правила, описывающие получение недостающих реквизитов. Как только все реквизиты будут получены, make вернется к выполнению отложенной цели. Отсюда следует, что make выполняет правила рекурсивно.

Фиктивные цели

На самом деле, в качестве make целей могут выступать не только реальные файлы. Все, кому приходилось собирать программы из исходных кодов должны быть знакомы с двумя стандартными в мире UNIX командами:

Командой make производят компиляцию программы, командой make install — установку. Такой подход весьма удобен, поскольку все необходимое для сборки и развертывания приложения в целевой системе включено в один файл (забудем на время о скрипте configure). Обратите внимание на то, что в первом случае мы не указываем цель, а во втором целью является вовсе не создание файла install, а процесс установки приложения в систему. Проделывать такие фокусы нам позволяют так называемые фиктивные (phony) цели. Вот краткий список стандартных целей:

- all — является стандартной целью по умолчанию. При вызове make ее можно явно не указывать.

- clean — очистить каталог от всех файлов полученных в результате компиляции.

- install — произвести инсталляцию

- uninstall — и деинсталляцию соответственно.

Для того чтобы make не искал файлы с такими именами, их следует определить в Makefile, при помощи директивы .PHONY. Далее показан пример Makefile с целями all, clean, install и uninstall:

Теперь мы можем собрать нашу программу, произвести ее инсталлцию/деинсталляцию, а так же очистить рабочий каталог, используя для этого стандартные make цели.

Обратите внимание на то, что в цели all не указаны команды; все что ей нужно — получить реквизит hello. Зная о рекурсивной природе make, не сложно предположить как будет работать этот скрипт. Так же следует обратить особое внимание на то, что если файл hello уже имеется (остался после предыдущей компиляции) и его реквизиты не были изменены, то команда make ничего не станет пересобирать. Это классические грабли make. Так например, изменив заголовочный файл, случайно не включенный в список реквизитов, можно получить долгие часы головной боли. Поэтому, чтобы гарантированно полностью пересобрать проект, нужно предварительно очистить рабочий каталог:

Для выполнения целей install/uninstall вам потребуются использовать sudo.

Переменные

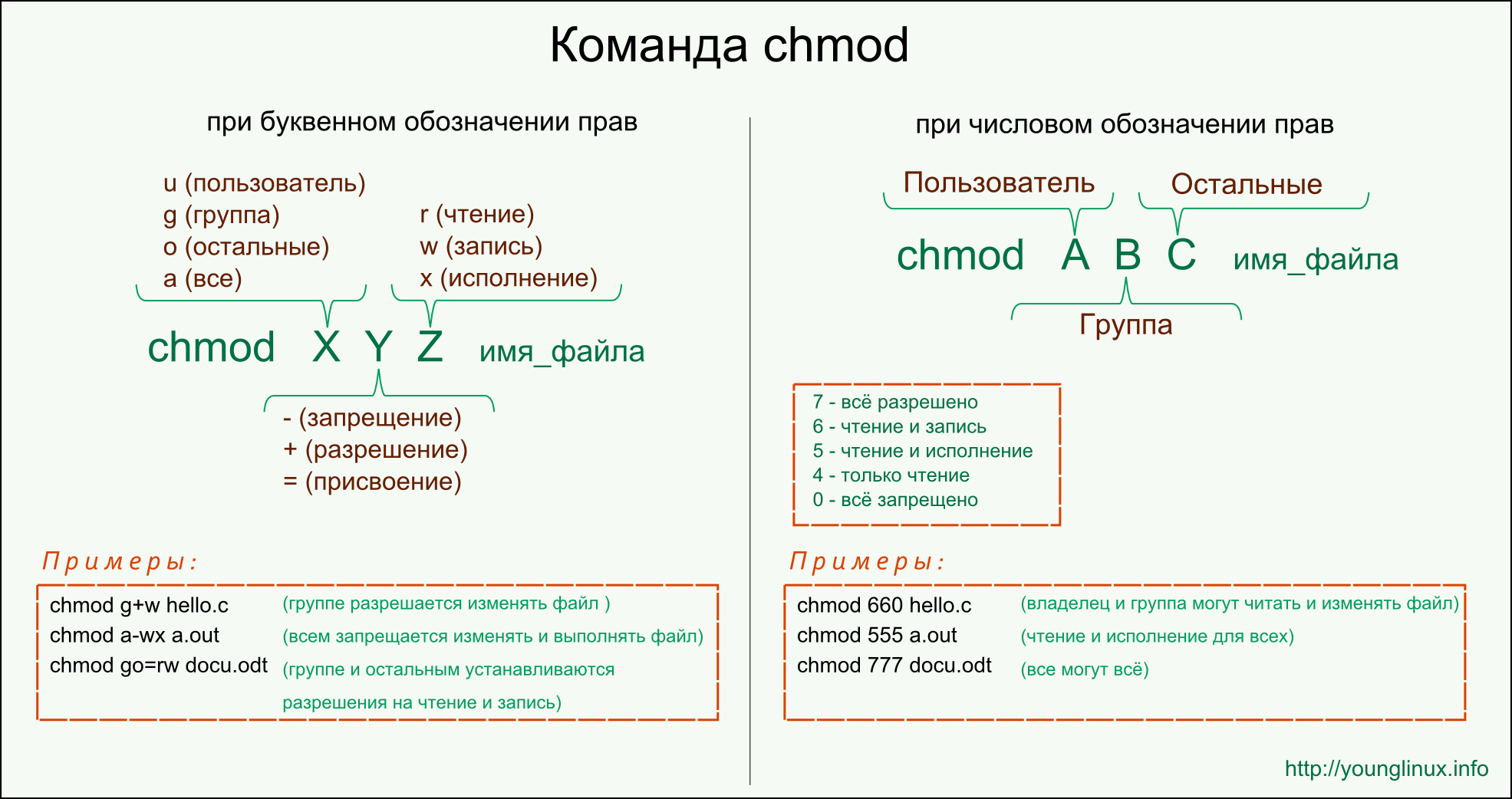

Все те, кто знакомы с правилом DRY (Don’t repeat yourself), наверняка уже заметили неладное, а именно — наш Makefile содержит большое число повторяющихся фрагментов, что может привести к путанице при последующих попытках его расширить или изменить. В императивных языках для этих целей у нас имеются переменные и константы; make тоже располагает подобными средствами. Переменные в make представляют собой именованные строки и определяются очень просто:

Существует негласное правило, согласно которому следует именовать переменные в верхнем регистре, например:

Так мы определили список исходных файлов. Для использования значения переменной ее следует разименовать при помощи конструкции $( ); например так:

Ниже представлен мэйкфайл, использующий две переменные: TARGET — для определения имени целевой программы и PREFIX — для определения пути установки программы в систему.

Это уже посимпатичней. Думаю, теперь вышеприведенный пример для вас в особых комментариях не нуждается.

Автоматические переменные

Автоматические переменные предназначены для упрощения мейкфайлов, но на мой взгляд негативно сказываются на их читабельности. Как бы то ни было, я приведу здесь несколько наиболее часто используемых переменных, а что с ними делать (и делать ли вообще) решать вам:

Источник

How to Write and Run a C Program in Linux

Linux is becoming programming heaven for developers, being an open-source and free operating system. Turbo C compiler is already an old approach to compile programs so let us programmers move to Linux for a new programming environment. In this article, we will explain how to write, compile, and run a simple C program. This will serve as a basis for you to move to more complicated and useful C programs that you can write and execute on Linux.

We have run the steps and commands mentioned in this article on a Ubuntu 20.04 LTS system but it will work on other versions like Ubuntu 18.04 or distributions like Debian 10 in the exact same way.

We will be using the Linux command-line tool, the Terminal, in order to compile a simple C program. To open the Terminal, you can use the Ubuntu Dash or the Ctrl+Alt+T shortcut.

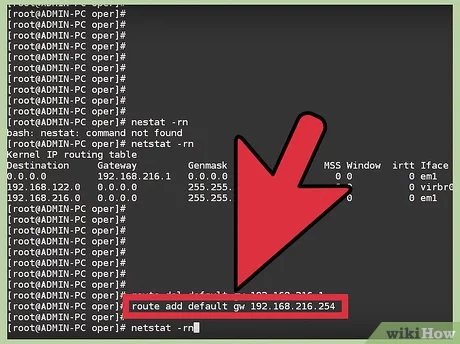

Step 1: Install the build-essential packages

In order to compile and execute a C program, you need to have the essential packages installed on your system. Enter the following command as root in your Linux Terminal:

You will be asked to enter the password for root; the installation process will begin after that. Please make sure that you are connected to the internet.

Step 2: Write a simple C program

After installing the essential packages, let us write a simple C program.

Open Ubuntu’s graphical Text Editor and write or copy the following sample program into it:

Then save the file with .c extension. In this example, I am naming my C program as sampleProgram.c

Alternatively, you can write the C program through the Terminal in gedit as follows:

This will create a .c file where you can write and save a program.

Step 3: Compile the C program with gcc Compiler

In your Terminal, enter the following command in order to make an executable version of the program you have written: Advertisement

Make sure your program is located in your Home folder. Otherwise, you will need to specify appropriate paths in this command.

Step 4: Run the program

The final step is to run the compiled C program. Use the following syntax to do so:

You can see how the program is executed in the above example, displaying the text we wrote to print through it.

Through this article, you have learned how to write, compile and run a simple C program in Linux. All you need is the essential packages and the right skills to make you a programming guru in Linux!

Karim Buzdar

About the Author: Karim Buzdar holds a degree in telecommunication engineering and holds several sysadmin certifications. As an IT engineer and technical author, he writes for various web sites. You can reach Karim on LinkedIn

Источник

Linux make command

On Unix-like operating systems, make is a utility for building and maintaining groups of programs (and other types of files) from source code.

This page covers the GNU/Linux version of make.

Description

The purpose of the make utility is to determine automatically which pieces of a large program need to be re-compiled, and issue the commands necessary to recompile them. This documentation describes the GNU implementation of make, which was written by Richard Stallman and Roland McGrath, and is currently maintained by Paul Smith. Many of the examples listed below show C programs, since they are most common, but you can use make with any programming language whose compiler can be run with a shell command. In fact, make is not limited to programs. You can use it to describe any task where some files must be updated automatically from others whenever the others change.

To prepare to use make, you must write a file called the makefile that describes the relationships among files in your program, and the states the commands for updating each file. In a program, typically the executable file is updated from object files, which are in turn made by compiling source files.

Once a suitable makefile exists, each time you change some source files, this simple shell command:

suffices to perform all necessary recompilations. The make program uses the makefile data base and the last-modification times of the files to decide which of the files need to be updated. For each of those files, it issues the commands recorded in the database.

make executes commands in the makefile to update one or more target names, where name is typically a program. If no -f option is present, make will look for the makefiles GNUmakefile, makefile, and Makefile, in that order.

Normally you should call your makefile either makefile or Makefile. (The officially recommended name is Makefile because it appears prominently near the beginning of a directory listing, right near other important files such as README.) The first name checked, GNUmakefile, is not recommended for most makefiles. You should use this name if you have a makefile that is specific to GNU make, and will not be understood by other versions of make. If makefile is a dash («—«), the standard input is read.

make updates a target if it depends on prerequisite files that have been modified since the target was last modified, or if the target does not exist.

Syntax

Options

| -b, -m | These options are ignored, but included for compatibility with other versions of make. |

| -B, —always-make | Unconditionally make all targets. |

| -C dir, —directory=dir | Change to directory dir before reading the makefiles or doing anything else. If multiple -C options are specified, each is interpreted relative to the previous one: -C / -C etc is equivalent to -C /etc. This is typically used with recursive invocations of make. |

| -d | Print debugging information in addition to normal processing. The debugging information says which files are being considered for remaking, which file-times are being compared and with what results, which files actually need to be remade, which implicit rules are considered and that are applied; everything interesting about how make decides what to do. |

| —debug[=FLAGS] | Print debugging information in addition to normal processing. If the FLAGS are omitted, then the behavior is the same as if -d was specified. FLAGS may be a for all debugging output (same as using -d), b for basic debugging, v for more verbose basic debugging, i for showing implicit rules, j for details on invocation of commands, and m for debugging while remaking makefiles. |

| -e, —environment-overrides | Give variables taken from the environment precedence over variables from makefiles. |

| -f file, —file=file, —makefile=file | Use file as a makefile. |

| -i, —ignore-errors | Ignore all errors in commands executed to remake files. |

| -I dir, —include-dir=dir | Specifies a directory dir to search for included makefiles. If several -I options are used to specify several directories, the directories are searched in the order specified. Unlike the arguments to other flags of make, directories given with -I flags may come directly after the flag: -Idir is allowed, as well as -I dir. This syntax is allowed for compatibility with the C preprocessor’s -I flag. |

| -j [jobs], —jobs[=jobs] | Specifies the number of jobs (commands) to run simultaneously. If there is more than one -j option, the last one is effective. If the -j option is given without an argument, make will not limit the number of jobs that can run simultaneously. |

| -k, —keep-going | Continue as much as possible after an error. While the target that failed (and those that depend on it) cannot be remade, the other dependencies of these targets can be processed all the same. |

| -l [load], —load-average[=load] | Specifies that no new jobs (commands) should be started if there are others jobs running and the load average is at least load (a floating-point number). With no argument, removes a previous load limit. |

| -L, —check-symlink-times | Use whichever is the latest modification time between symlinks and target. |

| -n, —just-print, —dry-run, —recon | Print the commands that would be executed, but do not execute them. |

| -o file, —old-file=file, —assume-old=file | Do not remake the file file even if it is older than its dependencies, and do not remake anything on account of changes in file. Essentially the file is treated as very old and its rules are ignored. |

| -p, —print-data-base | Print the database (rules and variable values) that results from reading the makefiles; then execute as usual or as otherwise specified. This also prints the version information given by the -v switch (see below). To print the database without trying to remake any files, use make -p -f/dev/null. |

| -q, —question | «Question mode.» Do not run any commands, or print anything; just return an exit status that is zero if the specified targets are already up to date, nonzero otherwise. |

| -r, —no-builtin-rules | Eliminate use of the built-in implicit rules. Also, clear out the default list of suffixes for suffix rules. |

| -R, —no-builtin-variables | Don’t define any built-in variables. |

| -s, —silent, —quiet | Silent operation; do not print the commands as they are executed. |

| -S, —no-keep-going, —stop | Cancel the effect of the -k option. This is never necessary except in a recursive make where -k might be inherited from the top-level make via MAKEFLAGS or if you set -k in MAKEFLAGS in your environment. |

| -t, —touch | Touch files (mark them up to date without really changing them) instead of running their commands. This is used to pretend that the commands were done, to fool future invocations of make. |

| -v, —version | Print the version of make; also a Copyright, a list of authors and a notice that there is no warranty. |

| -w, —print-directory | Print a message containing the working directory before and after other processing. This may be useful for tracking down errors from complicated nests of recursive make commands. |

| —no-print-directory | Turn off -w, even if it was turned on implicitly. |

| -W file, —what-if=file, —new-file=file, —assume-new=file | Pretend that the target file has just been modified. When used with the -n flag, this shows you what would happen if you were to modify that file. Without -n, it is almost the same as running a touch command on the given file before running make, except that the modification time is changed only internally within make. |

| —warn-undefined-variables | Warn when an undefined variable is referenced. |

Typical Use

make is typically used to build executable programs and libraries from source code. Generally speaking, make is applicable to any process that involves executing arbitrary commands to transform a source file to a target result. For example, make could be used to detect a change made to an image file (the source) and the transformation actions might be to convert the file to some specific format, copy the result into a content management system, and then send e-mail to a predefined set of users that the above actions were performed.

make is invoked with a list of target file names to build as command-line arguments:

Without arguments, make builds the first target that appears in its makefile, which is traditionally a target named all.

make decides whether a target needs to be regenerated by comparing file modification times. This solves the problem of avoiding the building of files that are already up to date, but it fails when a file changes but its modification time stays in the past. Such changes could be caused by restoring an older version of a source file, or when a network filesystem is a source of files and its clock or timezone is not synchronized with the machine running make. The user must handle this situation by forcing a complete build. Conversely, if a source file’s modification time is in the future, it may trigger unnecessary rebuilding.

Makefiles

make searches the current directory for the makefile to use. GNU make searches files for a file named one of GNUmakefile, makefile, and then Makefile, and runs the specified target(s) from that file.

The makefile language is similar to declarative programming, in which necessary end conditions are described but the order in which actions are to be taken is not important. This may be confusing to programmers used to imperative programming, which explicitly describes how the end result will be reached.

One problem in build automation is the tailoring of a build process to a given platform. For instance, the compiler used on one platform might not accept the same options as the one used on another. This is not well handled by make on its own. This problem is typically handled by generating separate platform-specific build instructions, which in turn may be processed by make. Common tools for this process are autoconf and cmake.

Rules

A makefile essentially consists of rules. Each rule begins with a dependency line which defines a target followed by a colon («:«) and optionally an enumeration of components (files or other targets) on which the target depends. The dependency line is arranged so that the target (left hand of the colon) depends on components (right hand of the colon). It is common to refer to components as prerequisites of the target.

Here, is the tab character. Usually each rule has a single unique target, rather than multiple targets.

For example, a C .o object file is created from .c files, so .c files come first (i.e. specific object file target depends on a C source file and header files). Because make itself does not understand, recognize or distinguish different kinds of files, this opens up the possibility for human error. A forgotten or an extra dependency may not be immediately obvious and may result in subtle bugs in the generated software. It is possible to write makefiles which generate these dependencies by calling third-party tools, and some makefile generators, such as the GNU automake toolchain, can do so automatically.

After each dependency line, a series of command lines may follow which define how to transform the components (usually source files) into the target (usually the «output»). If any of the components have been modified, the command lines are run.

With GNU make, the first command may appear on the same line after the prerequisites, separated by a semicolon:

Each command line must begin with a tab character to be recognized as a command. The tab is a whitespace character, but the space character does not have the same special meaning. This is problematic, since there may be no visual difference between a tab and a series of space characters. This aspect of the syntax of makefiles is often subject to criticism, and is important to take note.

However, GNU make (since version 3.82) allows the user to choose any symbol (one character) as the recipe prefix using the .RECIPEPREFIX special variable, for example:

Each command is executed by a separate shell or command-line interpreter instance. Since operating systems use different command-line interpreters this can lead to unportable makefiles. For instance, GNU make by default executes commands with /bin/sh, which is the shell where Unix commands like cp are normally used.

A rule may have no command lines defined. The dependency line can consist solely of components that refer to targets, for example:

The command lines of a rule are usually arranged so that they generate the target. An example: if «file.html» is newer, it is converted to text. The contents of the makefile:

The above rule would be triggered when make updates «file.txt«.

In the following invocation, make would typically use this rule to update the «file.txt» target if «file.html» were newer:

Command lines can have one or more of the following three prefixes:

- a hyphen-minus (—), specifying that errors are ignored

- an at sign (@), specifying that the command is not printed to standard output before it is executed

- a plus sign (+), the command is executed even if make is invoked in a «do not execute» mode

Ignoring errors and silencing all echo output can also be obtained via the special targets «.IGNORE» and «.SILENT«, respectively.

Macros

A makefile can contain definitions of macros. Macros are usually referred to as variables when they hold simple string definitions, like «CC=clang«, which would specify clang as the C compiler. Macros in makefiles may be overridden in the command-line arguments passed to the make utility. environment variables are also available as macros.

Macros allow users to specify the programs invoked and other custom behavior during the build process. For example, as just shown, the macro «CC» is frequently used in makefiles to refer to the location of a C compiler.

New macros are traditionally defined using capital letters:

A macro is used by expanding it. Traditionally this is done by enclosing its name inside $(). An equivalent form uses curly braces rather than parenthesis, i.e. $<>, which is the style used in BSD operating systems.

Macros can be composed of shell commands using the command substitution operator, denoted by backticks («` `«).

The content of the definition is stored «as is». Lazy evaluation is used, meaning that macros are normally expanded only when their expansions are actually required, such as when used in the command lines of a rule. For example:

The generic syntax for overriding macros on the command line is:

Makefiles can access any of a number of predefined internal macros, with «?» and «@» being the most common.

Источник